Microchip PIC32MX120F032D Handleiding

Microchip Niet gecategoriseerd PIC32MX120F032D

Bekijk gratis de handleiding van Microchip PIC32MX120F032D (84 pagina’s), behorend tot de categorie Niet gecategoriseerd. Deze gids werd als nuttig beoordeeld door 32 mensen en kreeg gemiddeld 4.8 sterren uit 8 reviews. Heb je een vraag over Microchip PIC32MX120F032D of wil je andere gebruikers van dit product iets vragen? Stel een vraag

Pagina 1/84

2007-2021 Microchip Technology Inc.DS60001145AA-page 1

PIC32

1.0DEVICE OVERVIEW

This document defines the Flash programming

specification for the PIC32 family of 32-bit

microcontrollers.

This programming specification is designed to guide

developers of external programmer tools. Customers

who are developing applications for PIC32 devices

should use development tools that already provide

support for device programming.

The major topics of discussion include:

•Section 1.0 “Device Overview”

•Section 2.0 “Programming Overview”

•Section 3.0 “Programming Steps”

•Section 4.0 “Connecting to the Device”

•Section 5.0 “EJTAG vs. ICSP”

•Section 6.0 “Pseudo Operations”

•Section 7.0 “Entering 2-Wire Enhanced ICSP

Mode”

•Section 8.0 “Check Device Status”

•Section 9.0 “Erasing the Device”

•Section 10.0 “Entering Serial Execution Mode”

•Section 11.0 “Downloading the Programming

Executive (PE)”

•Section 12.0 “Downloading a Data Block”

•Section 13.0 “Initiating a Page Erase”

•Section 14.0 “Initiating a Flash Row Write”

•Section “”

•Section 16.0 “Exiting Programming Mode”

•Section 17.0 “The Programming Executive”

•Section 18.0 “Checksum”

•Section 19.0 “Configuration Memory and Device

ID”

•Section 20.0 “TAP Controllers”

•Section 21.0 “AC/DC Characteristics and Timing

Requirements”

•Appendix A: “PIC32 Flash Memory Map”

•Appendix B: “Hex File Format”

•Appendix C: “Device IDs”

•Appendix D: “Revision History”

2.0PROGRAMMING OVERVIEW

When in development of a programming tool, it is

necessary to understand the internal Flash program

operations of the target device and the Special

Function Registers (SFRs) used to control Flash

programming, as these same operations and registers

are used by an external programming tool and its

software. These operations and control registers are

described in the “Flash Program Memory” chapter in

the specific device data sheet, and the related “PIC32

Family Reference Manual”section. It is highly

recommended that these documents be used in

conjunction with this programming specification.

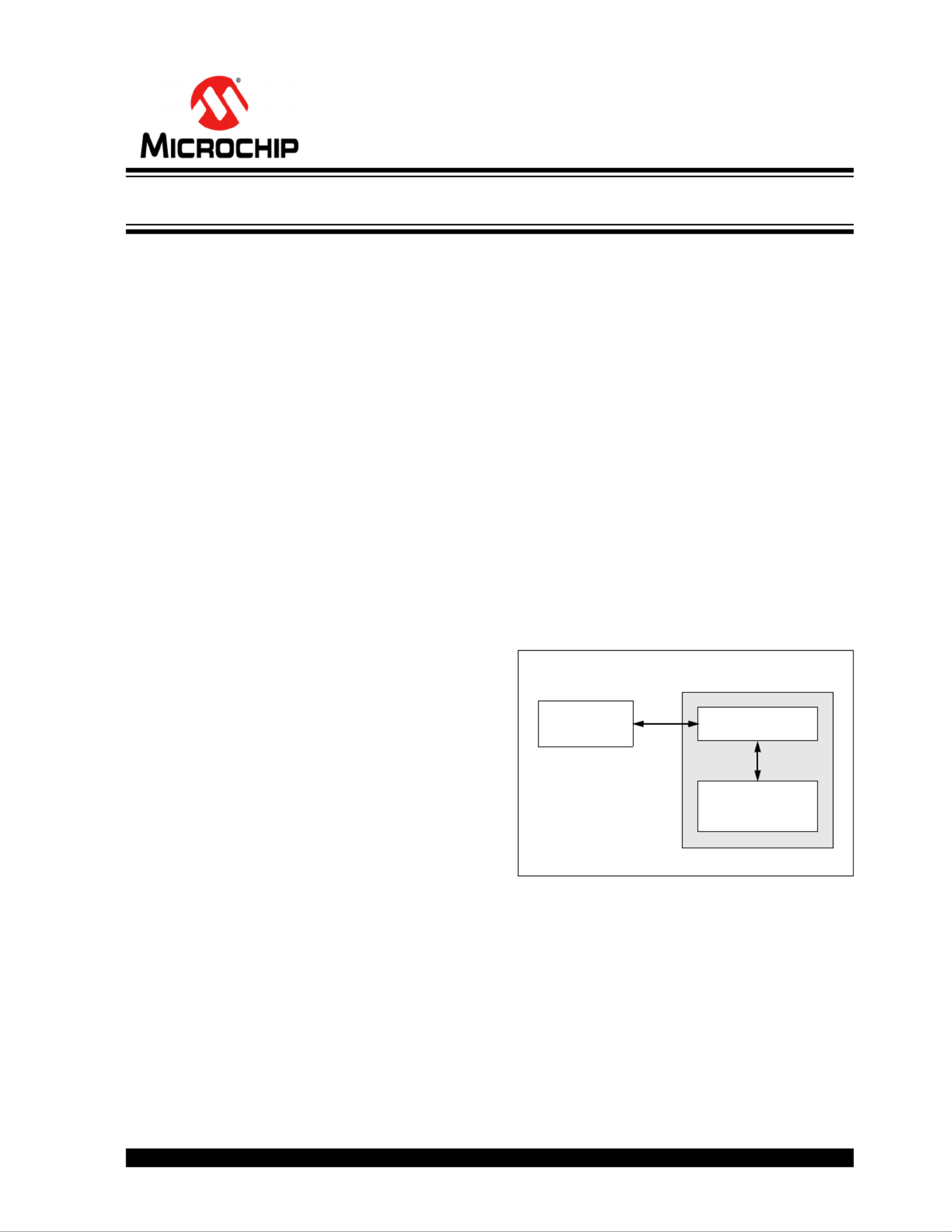

An external tool programming setup consists of an

external programmer tool and a target PIC32 device.

Figure 2-1 illustrates a typical programming setup. The

programmer tool is responsible for executing

necessary programming steps and completing the

programming operation.

FIGURE 2-1:PROGRAMMING SYSTEM

SETUP

Target PIC32 Device

CPU

On-Chip Memory

External

Programmer

PIC32 Flash Programming Specification

Product specificaties

| Merk: | Microchip |

| Categorie: | Niet gecategoriseerd |

| Model: | PIC32MX120F032D |

Heb je hulp nodig?

Als je hulp nodig hebt met Microchip PIC32MX120F032D stel dan hieronder een vraag en andere gebruikers zullen je antwoorden

Handleiding Niet gecategoriseerd Microchip

2 Februari 2026

26 Januari 2026

13 Januari 2026

12 Januari 2026

12 Januari 2026

12 Januari 2026

12 Januari 2026

12 Januari 2026

6 December 2025

5 December 2025

Handleiding Niet gecategoriseerd

Nieuwste handleidingen voor Niet gecategoriseerd

5 Mei 2026

5 Mei 2026

5 Mei 2026

5 Mei 2026

5 Mei 2026

5 Mei 2026

5 Mei 2026

5 Mei 2026

5 Mei 2026

5 Mei 2026